Overlapping Sequence Detector Verilog Code

1001 Sequence Detector Verilog Code

In this post we are going to discuss the Verilog code of 1001 sequence detector. The sequence detector is of overlapping type. It means that the sequencer keep track of the previous sequences. Whenever the sequencer finds the incoming sequence matches with the 1001 sequence it gives the output 1.

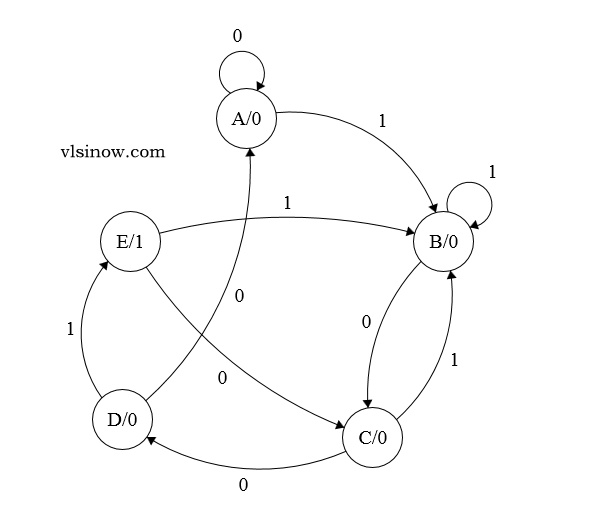

As Moore machine is used mostly in all practical designs the Verilog code for 1001 sequence detector fsm is written in Moore fsm logic.

1001 Sequence Detector State Diagram is given below.

The verilog code for overlapping moore sequence detector is given below.

`timescale 10ns / 1ps

module moore_1001(

input reset,

input clk,

input x,

output reg y

);

parameter A=3'd0, B=3'd1, C=3'd2, D=3'd3, E=3'd4;

reg [2:0] current_State, next_State;

always @(posedge clk)

begin

if(reset)

current_State <=A;

else

current_State <=next_State;

end

always @(*)

begin

next_State= current_State;

y=1'b0;

case (current_State)

A: begin

if(x==1'b1) next_State=B;

end

B: begin

if(x==1'b0) next_State=C;

end

C: begin

if(x==1'b0) next_State=D;

else

next_State= B;

end

D: begin

if(x==1'b0) next_State=A;

else

next_State= E;

end

E:

begin

y=1'b1;

if(x==1'b0) next_State=C;

else

next_State= B;

end

default: begin next_State=A;

y=1'b0; end

endcase

end

endmodule

1001 Sequence Detector Simulation Result

If you have any query/suggestion please feel free to comment below the post.

how to see the output for the above program

You can use online EDA playground website