2:1 MUX Verilog Code

4:1 MUX Verilog Code

Multiplexer Verilog Code

In this post we are sharing with you the Verilog code of different multiplexers such as 2:1 MUX, 4:1 MUX etc.

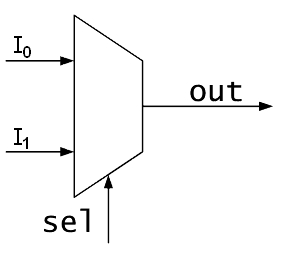

I am sure you are aware of with working of a Multiplexer. The general block level diagram of a Multiplexer is shown below.

When sel is at logic 0 out=I0 and when select is at logic 1 out=I1.

2:1 MUX Verilog in Data Flow Model is given below.

module mux2X1( in0,in1,sel,out);

input in0,in1, sel;

output out;

assign out=(sel)?in1:in0;

endmodule

//test bench

module mux2X1_tb;

reg in0, in1;

reg sel;

wire out;

mux2X1 uut(.in0(in0), .in1(in1),.sel(sel),.out(out));

initial begin

$monitor( "in0=%d, in1=%d, sel= %d, out=%d", in0,in1,sel,out);

for (int i=0; i<8; i=i+1) begin

{in0,in1,sel} = i;

#10;

end

end

endmodule

Verilog Code of 2:1 MUX in Behavioral Model is given below.

module mux2X1( in0,in1,sel,out);

input in0,in1, sel;

output reg out;

always @(*)

begin

if(sel)

out= in1;

else

out=in0;

end

endmodule

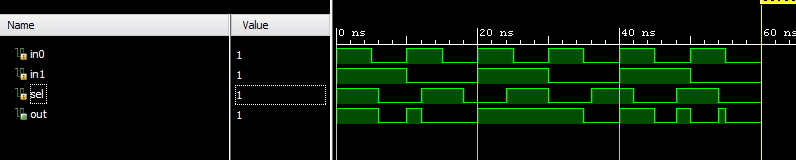

Simulation Result:

Now we are going to share with you the 4:1 MUX Verilog code in dataflow and behavioral.

4:1 MUX Verilog Code in Dataflow model is given below.

module mux4X1( in,sel,out); input [3:0]in; input [1:0]sel; output out; assign out = sel[1] ? ( sel[0] ? in[3]: in[2]) : ( sel[0] ? in[1]: in[0]); endmodule

4:1 MUX Verilog Code in Behavioral model is given below.

module mux4X1( in,sel,out); input [3:0]in; input [1:0]sel; output reg out; always @(*) begin case(sel) 2'b00: out=in[0]; 2'b01: out=in[1]; 2'b10: out=in[2]; 2'b11: out=in[3]; default: out=1'b0; endcase end endmodule

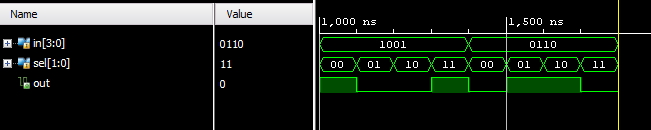

Simulation Result:

If you have any query/suggestion please feel free to comment below the post.